xenium

Member

I hope some of the experts here can help me bring another PET back from the dead!

I have a CBM 8032 (universal PET motherboard 8032089), which was dead when I purchased it (no video, no chirp.)

I bought one of Mike's (Bitfixer) ROMulators (a RAM/ROM replacement board for the 6502), and with the ROMulator in place the PET fired right up, and seemed to work properly.

So I began trying to narrow things down by re-enabling each of the ROMs and each of the RAM banks on the motherboard one by one. By doing so I discovered that all my ROMs are good, and that both banks of RAM have problems.

I also tried running the PETTESTE2K ROM in the PET (via the ROMulator, rather than an actual EPROM). The results were:

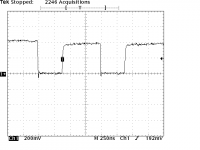

(1) With all the RAM on the motherboard enabled, the standard edit ROM won't boot (black screen, no chirp), and PETTEST fails the zero page test. Every 64th byte in the zero page test is correct however (I've been trying to wrap my brain around what that could mean, as far as stuck address lines or stuck RAM bits or what not?) Here's a photo of the zero page test results:

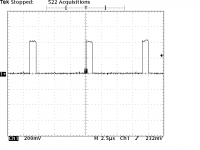

(2) With zero page ($0000 to $03FF actually) mapped to the ROMulator and the rest of the RAM on the motherboard enabled, the standard edit ROM boots, but BASIC reports 0 bytes free. PETTEST reports 4K, and then:

0..........

mem fail 0 0 0400 02 0f!

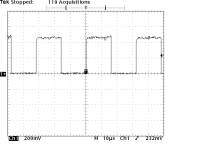

(3) With zero page and the rest of the first bank of RAM mapped to the ROMulator and only the second bank on the motherboard enabled, the standard edit ROM boots, but BASIC reports 15359 bytes free. PETTEST reports 16K, and the 16K passes tests.

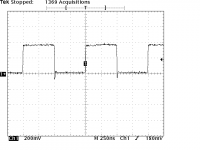

So it seems like I either have problems with both banks of RAM, or possibly with the 74LS244 chips that handle RAM addressing, CAS, and RAS (UE8, UE9, and UE10)?

This is where I hit the limits of my knowledge. I do have a scope (that I barely know how to use, lol), and looking at the above chips and the RAM chips, I see "stuff" that looks normal to me (-5, +5, +12 where it should be, and activity on all the other pins that are shown connected on the schematics.) Some of the levels look low, some even a tad below 4V, but that should still be within TTL specs I think? None of the lines appear to be stuck in a high or low state.

Is there a way to troubleshoot this further without resorting to desoldering all those chips? I do have a proper desoldering iron (that I barely know how to use... there's a pattern here, lol), but that's 316 pins, if I did my math right.

PETTEST's RAM test will provide enough detail to identify which specific RAM chip is causing a problem, but unfortunately it won't even test the RAM, because it's failing badly enough that PETTEST doesn't recognize it (PETTEST simply does a write/read test on the first byte of each bank to determine if there is RAM there to test, and since mine fails, it thinks there's no RAM there and won't do a detailed test of it.) Is there a better RAM test program I should use?

Thanks for any ideas!

I have a CBM 8032 (universal PET motherboard 8032089), which was dead when I purchased it (no video, no chirp.)

I bought one of Mike's (Bitfixer) ROMulators (a RAM/ROM replacement board for the 6502), and with the ROMulator in place the PET fired right up, and seemed to work properly.

So I began trying to narrow things down by re-enabling each of the ROMs and each of the RAM banks on the motherboard one by one. By doing so I discovered that all my ROMs are good, and that both banks of RAM have problems.

I also tried running the PETTESTE2K ROM in the PET (via the ROMulator, rather than an actual EPROM). The results were:

(1) With all the RAM on the motherboard enabled, the standard edit ROM won't boot (black screen, no chirp), and PETTEST fails the zero page test. Every 64th byte in the zero page test is correct however (I've been trying to wrap my brain around what that could mean, as far as stuck address lines or stuck RAM bits or what not?) Here's a photo of the zero page test results:

(2) With zero page ($0000 to $03FF actually) mapped to the ROMulator and the rest of the RAM on the motherboard enabled, the standard edit ROM boots, but BASIC reports 0 bytes free. PETTEST reports 4K, and then:

0..........

mem fail 0 0 0400 02 0f!

(3) With zero page and the rest of the first bank of RAM mapped to the ROMulator and only the second bank on the motherboard enabled, the standard edit ROM boots, but BASIC reports 15359 bytes free. PETTEST reports 16K, and the 16K passes tests.

So it seems like I either have problems with both banks of RAM, or possibly with the 74LS244 chips that handle RAM addressing, CAS, and RAS (UE8, UE9, and UE10)?

This is where I hit the limits of my knowledge. I do have a scope (that I barely know how to use, lol), and looking at the above chips and the RAM chips, I see "stuff" that looks normal to me (-5, +5, +12 where it should be, and activity on all the other pins that are shown connected on the schematics.) Some of the levels look low, some even a tad below 4V, but that should still be within TTL specs I think? None of the lines appear to be stuck in a high or low state.

Is there a way to troubleshoot this further without resorting to desoldering all those chips? I do have a proper desoldering iron (that I barely know how to use... there's a pattern here, lol), but that's 316 pins, if I did my math right.

PETTEST's RAM test will provide enough detail to identify which specific RAM chip is causing a problem, but unfortunately it won't even test the RAM, because it's failing badly enough that PETTEST doesn't recognize it (PETTEST simply does a write/read test on the first byte of each bank to determine if there is RAM there to test, and since mine fails, it thinks there's no RAM there and won't do a detailed test of it.) Is there a better RAM test program I should use?

Thanks for any ideas!