"LDIR" is the Z80 "block move" instruction, basically it copies the number of bytes in the BC register pair from the address in HL to the address in DE. It is the fastest way to copy a block of memory using software (a DMA controller could do that much faster).

The XMOVE is a BIOS entry defined for banked CP/M 3 BIOSes, it sets up a cross-bank move operation. You should read the DRI CP/M 3 System manual carefully to fully understand what needs to be implemented. The XMOVE call simply tells the BIOS that the *next* call to MOVE should use the inter-bank data provided.

The banked version of CP/M 3 (BNKBDOS3) determines whether XMOVE is supported, and will use that to move data to/from system buffers when needed. The existence of this features allows disk buffers to be in bank 0 instead of requiring them to be in common memory.

Regarding the 74LS612, from what I see it is a DIP40 device. That takes up a lot of PCB real state, and using two of them takes up even more. I'm not sure what you space budget is, though. As you already mentioned, you are reducing the number of MMU registers you must update when switching banks, so not all 16 MMU registers are being used. It's a trade-off, but you may want to consider supporting XMOVE.

Also, if you are not locked-in to using the 74LS612, I think you could use a different approach that takes less space on the PCB and requires fewer OUT instructions to change banks. While reading through the Z180 datasheets in order to understand it's MMU is probably a long detour, you could basically implement that using a 4-bit output port to select the common memory boundary (or you could hard-code it with dipswitches), then use a 4-bit comparator like the 74LS85 to see if CPU address bits A12-A15 indicate common or banked memory. Then you could use an 8-bit port, or two, to select the bank address. You could also use a fast adder to allow more flexible selection of the physical memory used for each bank, and less wasted memory.

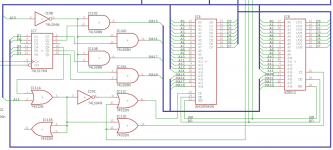

A very simple/crude example is here,

http://sims.durgadas.com/kaypro/ram256k.pdf, that I did back in 1986 for a Kaypro machine. Because I needed to support DRAM refresh, and only had 256K RAM, that schematic is not what you'd want to use but it might demonstrate the general idea. There's a little description of that circuit at

http://sims.durgadas.com/kaypro/kaypro84x.html under "Memory Modification". Note, that circuit would waste the "duplicate" common memory of each bank (extremely simplistic bank select), but using an adder to combine a base address would allow each bank to better utilize all of memory.