Some weeks ago I had some random thoughts about how difficult would be interfacing some SRAM chips to the ISA bus of a 8088 motherboard. The main idea was to give use to two 62256 ICs I had lying around. This week I had some time to wrote a small schematic in a sheet of paper and begin to build it.

As I had a spare ISA card to canibalize (the one from this post) and it included some 74LS chips that I needed, and also other two 62256-compatible ICs, it would be an "almost cost 0" project.

Using four 62256 would give me 128 kilobytes to start messing around. The logic is very simple, a 74LS139 to enable the /CS line of each SRAM IC, a 74LS688 wired to a block of dip switches to set the memory range, a 74LS68 to do a XOR of /MEMR and /MEMW lines and a 70LS04 to negate it and feed the /G of the 74LS688 with that.

I wanted to address manually the contiguous 128 kb in any consecutive bank pair. That would let me:

- Set the SRAM from 00000h to 1FFFFh, removing all the 4164s and 41256s onboard so the only RAM is the SRAM.

- Mix SRAM and DRAM, removing only the 4164s from banks 3 & 4 onboard and setting the SRAM to 80000h to 9FFFFh. That would be 640 kb (512 kb DRAM and 128 kb SRAM).

- Set the SRAM in the Upper Memory range (D0000 to EFFFF) and use it with some external drivers. I think there are some drivers available to get a UMB to load TSRs or a ramdisk, and disk-cache programs that can use upper memory. I still have to investigate it, but it seems to be the most interesting option. Another cool thing would be to load DOS into this memory freeing up conventional memory, but I don't think a XT can perform it.

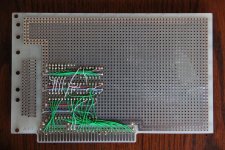

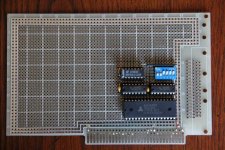

Here it is the result. The card is very ugly, don't be afraid :lol:

Click to enlarge

Any suggestions or comments to share?

As I had a spare ISA card to canibalize (the one from this post) and it included some 74LS chips that I needed, and also other two 62256-compatible ICs, it would be an "almost cost 0" project.

Using four 62256 would give me 128 kilobytes to start messing around. The logic is very simple, a 74LS139 to enable the /CS line of each SRAM IC, a 74LS688 wired to a block of dip switches to set the memory range, a 74LS68 to do a XOR of /MEMR and /MEMW lines and a 70LS04 to negate it and feed the /G of the 74LS688 with that.

I wanted to address manually the contiguous 128 kb in any consecutive bank pair. That would let me:

- Set the SRAM from 00000h to 1FFFFh, removing all the 4164s and 41256s onboard so the only RAM is the SRAM.

- Mix SRAM and DRAM, removing only the 4164s from banks 3 & 4 onboard and setting the SRAM to 80000h to 9FFFFh. That would be 640 kb (512 kb DRAM and 128 kb SRAM).

- Set the SRAM in the Upper Memory range (D0000 to EFFFF) and use it with some external drivers. I think there are some drivers available to get a UMB to load TSRs or a ramdisk, and disk-cache programs that can use upper memory. I still have to investigate it, but it seems to be the most interesting option. Another cool thing would be to load DOS into this memory freeing up conventional memory, but I don't think a XT can perform it.

Here it is the result. The card is very ugly, don't be afraid :lol:

Click to enlarge

Any suggestions or comments to share?