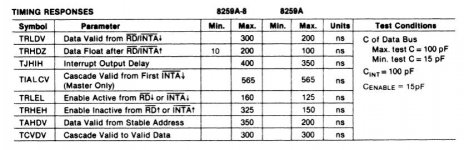

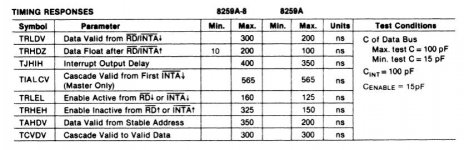

Please can anyone confirm if I'm reading these datasheets correctly:

8259A "Data Valid From RD/INTA": Max 200ns so the max speed is 5.0Mhz?

8259A-2 "Data Valid From RD/INTA": Max 120ns so the max speed is 8.3Mhz? (not shown)

8259A-8 "Data Valid From RD/INTA": Max 300ns so the max speed is 3.3Mhz?

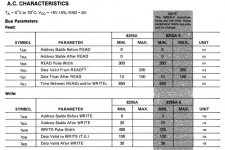

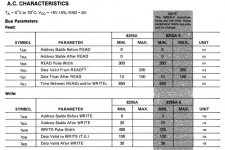

On page 473 of the data catalog:

8255A "Data Valid From READ": Max 250ns so the max speed is 4Mhz?

8255A-5 "Data Valid From READ": Max 200ns so the max speed is 5Mhz?

On page 590 of the data catalog:

Source:

ftp://bitsavers.informatik.uni-stut...taBooks/1979_Intel_Component_Data_Catalog.pdf

8259A "Data Valid From RD/INTA": Max 200ns so the max speed is 5.0Mhz?

8259A-2 "Data Valid From RD/INTA": Max 120ns so the max speed is 8.3Mhz? (not shown)

8259A-8 "Data Valid From RD/INTA": Max 300ns so the max speed is 3.3Mhz?

On page 473 of the data catalog:

8255A "Data Valid From READ": Max 250ns so the max speed is 4Mhz?

8255A-5 "Data Valid From READ": Max 200ns so the max speed is 5Mhz?

On page 590 of the data catalog:

Source:

ftp://bitsavers.informatik.uni-stut...taBooks/1979_Intel_Component_Data_Catalog.pdf