mrmanse

Member

Hi everyone!

If in a hurry, my questions are at the end.

So I bought an old 5170 a few years back at auction, with more or less unknown condition. I recently started working on the machine, which at first was dead, and quite badly corroded. The PSU was dead, but I located a failed LM324 circuit (IC0004), which fixed the problem. I made a schematic of the top PCB in the PSU, much like with the 5150 recently posted, but this one is needs some more work before ready for publication. If anyone should need it as is, just contact me.

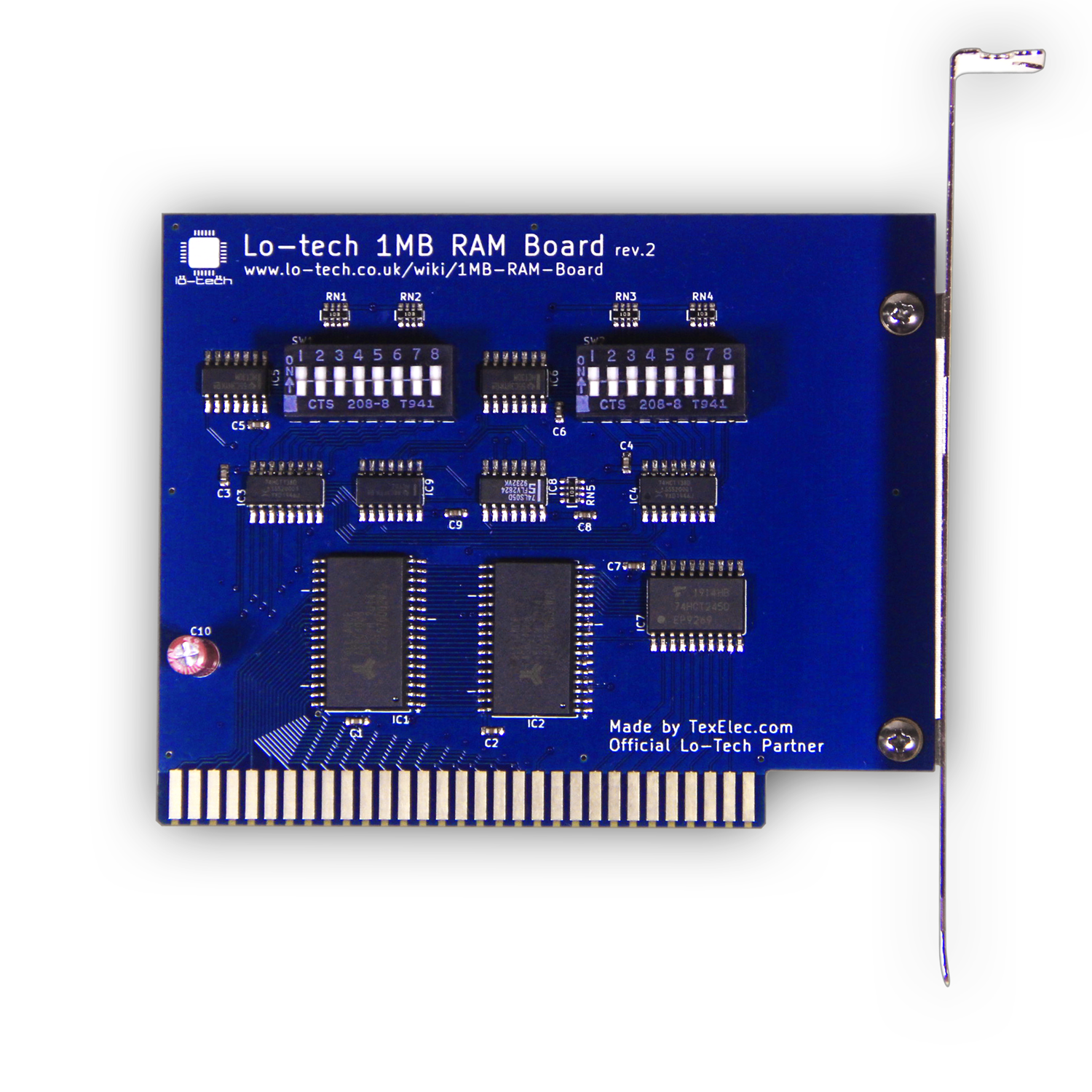

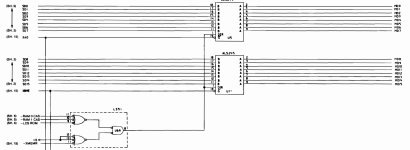

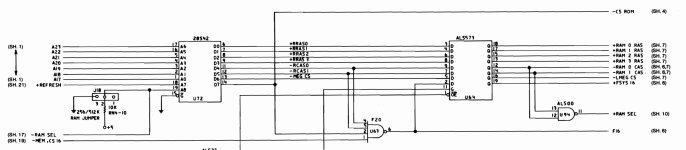

Well, after I got the PSU working, the mobo was dead. I made BIOS replacement with two flash chips (29EE011 type) and put the Supersoft diagnostics on there. It ran quite unreliably, and never past the 16KB critical memory test. I replaced the corroded U27 and U47 IC sockets which at least made it run stably, but the memory issue remained. So I did the wiggle maneuver but with no luck. Unfortunately for me this was a type 1 motherboard with only 256KB on board, and I have no spare piggyback DRAMs. So I made a few suitable DRAMS by stacking some 4164 DRAMs (pins 1-3 needs some tweaking, but it's doable). Same result, seemed like many of the chips were bad and I couldn't identify which ones. I then got the idea of a complete memory replacement for the IBM 5170. Did a test with a 5V-tolerant 256kb x 16 dram laying around, and it kind of worked, at least partly. I got past the 16kB critical test, but it failed on the CPU protected mode (not the "normal" variant described by modem7, but the word Failed both on top of the screen AND in the column where it should say passed). It failed even worse with memory refresh tests, which isn't that surprising considering this was a completely different type of DRAM. So I started working on a SRAM replacement. It also isn't ready for publication, but I'll gladly share it in few weeks at most. It's based on 2 512kb x 8 SRAMs (yes, twice whats needed, but there are no 256kB x 8 ). It worked better than the DRAM variant, and passed Supersoft memory testing up till 0x40000, where it failed on bits 0, 2 and 5. I've never had a 5170 before so it took me a while to realize that it was the 256/512kB jumper set in the wrong position. After correct jumpering the Supersoft passed ALL tests, from to to bottom - YEAH!

). It worked better than the DRAM variant, and passed Supersoft memory testing up till 0x40000, where it failed on bits 0, 2 and 5. I've never had a 5170 before so it took me a while to realize that it was the 256/512kB jumper set in the wrong position. After correct jumpering the Supersoft passed ALL tests, from to to bottom - YEAH!

I then fixed a 6V battery (simply four 1,5V batteries in series), and set the correct settings in CBASIC using the GSETUP_BASIC app. Then troubles started.

1. The BIOS only identifies 384KB ram, both IBM 1984 BIOS and the AMI bios downloadable from minus zero degrees. This doesn't appear to be a configurable setting. I've tried to set it to 512KB, but I get the 203 error. Supersoft identifies and passes 512KB of RAM, but NOT if I a serial/parallell adapter is in ISA slot 2. I that card is in, Supersoft tests successfully up to 0x80000 (or 0x7FFFF) and then continues counting (and failing of course, even showing garbage on screen).

2. I have booted the machine to dos a few times, but it's unstable. I very soon get a parity error. So my plan is of course to get rid of the four remaining piggyback DRAMs used for parity and replacing them with parity calculating circuitry instead. There shouldn't ever be a parity error then, and with modern SRAMS on a enthusiast computer this safety isn't needed.

So - my questions - HOW exacly does the 5170 type 1 mobo identify the amount of onboard memory. Where did it get the 384KB from? Can it be set somehow that I've missed? I have checked and double checked my SRAM board, but since Supersoft finds all the RAM I don't think thats it.

Any other ideas would also be much appreciated.

Note the extra PCB with a quad OR gate. A required modification.

If in a hurry, my questions are at the end.

So I bought an old 5170 a few years back at auction, with more or less unknown condition. I recently started working on the machine, which at first was dead, and quite badly corroded. The PSU was dead, but I located a failed LM324 circuit (IC0004), which fixed the problem. I made a schematic of the top PCB in the PSU, much like with the 5150 recently posted, but this one is needs some more work before ready for publication. If anyone should need it as is, just contact me.

Well, after I got the PSU working, the mobo was dead. I made BIOS replacement with two flash chips (29EE011 type) and put the Supersoft diagnostics on there. It ran quite unreliably, and never past the 16KB critical memory test. I replaced the corroded U27 and U47 IC sockets which at least made it run stably, but the memory issue remained. So I did the wiggle maneuver but with no luck. Unfortunately for me this was a type 1 motherboard with only 256KB on board, and I have no spare piggyback DRAMs. So I made a few suitable DRAMS by stacking some 4164 DRAMs (pins 1-3 needs some tweaking, but it's doable). Same result, seemed like many of the chips were bad and I couldn't identify which ones. I then got the idea of a complete memory replacement for the IBM 5170. Did a test with a 5V-tolerant 256kb x 16 dram laying around, and it kind of worked, at least partly. I got past the 16kB critical test, but it failed on the CPU protected mode (not the "normal" variant described by modem7, but the word Failed both on top of the screen AND in the column where it should say passed). It failed even worse with memory refresh tests, which isn't that surprising considering this was a completely different type of DRAM. So I started working on a SRAM replacement. It also isn't ready for publication, but I'll gladly share it in few weeks at most. It's based on 2 512kb x 8 SRAMs (yes, twice whats needed, but there are no 256kB x 8

I then fixed a 6V battery (simply four 1,5V batteries in series), and set the correct settings in CBASIC using the GSETUP_BASIC app. Then troubles started.

1. The BIOS only identifies 384KB ram, both IBM 1984 BIOS and the AMI bios downloadable from minus zero degrees. This doesn't appear to be a configurable setting. I've tried to set it to 512KB, but I get the 203 error. Supersoft identifies and passes 512KB of RAM, but NOT if I a serial/parallell adapter is in ISA slot 2. I that card is in, Supersoft tests successfully up to 0x80000 (or 0x7FFFF) and then continues counting (and failing of course, even showing garbage on screen).

2. I have booted the machine to dos a few times, but it's unstable. I very soon get a parity error. So my plan is of course to get rid of the four remaining piggyback DRAMs used for parity and replacing them with parity calculating circuitry instead. There shouldn't ever be a parity error then, and with modern SRAMS on a enthusiast computer this safety isn't needed.

So - my questions - HOW exacly does the 5170 type 1 mobo identify the amount of onboard memory. Where did it get the 384KB from? Can it be set somehow that I've missed? I have checked and double checked my SRAM board, but since Supersoft finds all the RAM I don't think thats it.

Any other ideas would also be much appreciated.

Note the extra PCB with a quad OR gate. A required modification.