monahan_z

Experienced Member

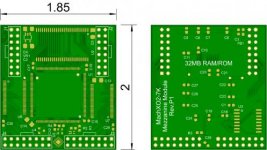

For people interested in building/repairing S-100 systems, Andrew Lynch at N8VEM and I at S100Computers.com have just completed a prototype of a new 80386 Master/Slave CPU board. This exciting board is capable of reaching up to12MHz in an S-100 system with an active terminated bus.

This is an ongoing project. It utilizes the 16 bit mode of the 80386 to address the 16MG of RAM the S-100 bus is capable of addressing. A second daughter board system with an overhead ribbon cable connector is planned to for daughter board(s) to enlarge the RAM space up to the 4GB the CPU is capable of addressing (using high density static and DRAM chips).

If you would like to read about this board please look here:-

http://s100computers.com/My System Pages/80386 Board/80386 CPU Board.htm

There is a growing list of people getting interested in these S-100 systems. We get these bare boards produced in batches (typically $20-40, depending on demand). We have done over 20 different types of S-100 boards so far! It is too early to accept “orders” for this board, but if you would like to be kept in the loop as this board evolves keep an eye on the above page.

This is an ongoing project. It utilizes the 16 bit mode of the 80386 to address the 16MG of RAM the S-100 bus is capable of addressing. A second daughter board system with an overhead ribbon cable connector is planned to for daughter board(s) to enlarge the RAM space up to the 4GB the CPU is capable of addressing (using high density static and DRAM chips).

If you would like to read about this board please look here:-

http://s100computers.com/My System Pages/80386 Board/80386 CPU Board.htm

There is a growing list of people getting interested in these S-100 systems. We get these bare boards produced in batches (typically $20-40, depending on demand). We have done over 20 different types of S-100 boards so far! It is too early to accept “orders” for this board, but if you would like to be kept in the loop as this board evolves keep an eye on the above page.