ExpandoRam Into IMSAI:

The way the jumper was drawn looked to be a IN-TRACE default jumper. In other words, no pins to jumper, just the trace on the back of the board so you can cut it if you really need to switch its connection.

Another thing I'd suggest is removing all the unnecessary boards from your IMSAI while looking at this DRAM problem. Using a MONITOR in EPROM would eliminate any likely DMA activity.

I suspect the problem comes down to the one-shots being out of spec. I was hoping the CHECK-OUT procedure would include testing those values, but it did not. No adjustments and 1970s fresh components and there was no reason for it to be tested.

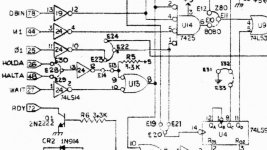

I'll look over the ExpandoRam-I schematics seriously next Saturday afternoon, if not before then. I have a few SBC-300s, SBC-200s, ExpandoRams-* and I think an I/O-8 from my days as SD Systems - so learning about their prior designs doesn't hurt.

Rev A may be a challenge. The PDF is for Rev E. I'll dig in my paper SD Systems Manuals tonight and see what I have. As I worked on their last Generation III board set, I doubt I have anything that old. Anyhow, probably just introduced all the jumpers when they discovered it wasn't quite the plug&play design they originally thought it was.

- - - - - - -

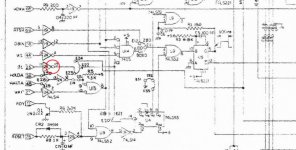

Those jumpers can be installed in a way that tie two output pins together. Trace out all the jumpers that are connected to the path from S100-25 (Phi 1) inward. If there is a jumper in the wrong place, two outputs could be tied together.

- - - - - - -

I assume this configuration was bundled by a previous owner. That doesn't mean it was all working fine when he put it away and years later decided to give it a new home. It might also be that he kept another memory board and inserted that one to fill in IMSAI bus. With so many years that a system like that could have been in storage, the previous owner might not even remember whether the ExpandoRam was the right memory board for his IMSAI.

I'd suggest the first thing you to is document all the jumper setting on the board. There are a lot of ways to configure one of these boards wrong.

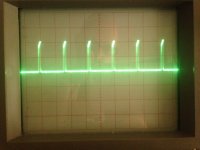

Check out the timing of U12 (a TTL Delay Line). I don't know how well those things age.

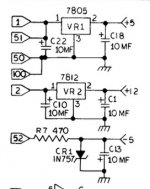

I also see a lot of dreaded one-shots on the board. The resistors and capacitors that establish its pulse width could easily be out of spec. My mentor at my first job said that the rule for digital design is: NO 555 timers, NO one-shots and NO monostable multivibrators... i.e everything should derive from an accurate clock signal.

User the ExpandoRam (1) manual, starting on page 7 through page 9, CHECK-OUT PROCEDURE to check the board out in the process of a check-out after build.

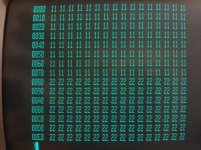

I recall that you previously wrote that you removed all but one bank of DRam for now...Note page 8 says, "*NOTE: If less than 32K is being installed on the board then refer to Section IV under ADDRESSING SWITCH to determine in which Bank the memory should be installed." Check that out in case there are some special configurations just for a single 16KByte Bank.

By the way, are you using a S-100 Board Extender? They caution not to use that during memory diagnostics... so that might be adding to the chaos.