westveld

Experienced Member

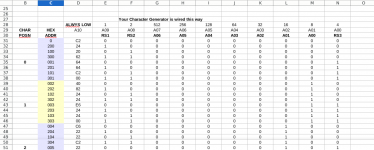

The SYSCOM II Apple II+ clone I've been working on is weird.

The ROMs data lines are wired like this:

Maybe they did this on purpose to avoid copyright somehow?

In the end the ROMs are almost identical to Apple's.

I dumped the ROMs and was confused - I expected almost identical to Apple II+ ROMs, but they are completely different.

And they don't match what the computer sees in monitor either.

I first assumed I goofed up the wiring on the ROM dumper, but no - dumped some other ROMs and they matched the expected images exactly.

Then assumed it was address lines not as expected, but nope - cheap logic analyzer on the data lines showed the expected ROM did send 1 thing out and the CPU got something different.

Ahah, take another look at comparing the binary of the monitor dump and the ROM dump and figure out the line flipping.

Sheesh

The ROMs data lines are wired like this:

Code:

CPU D0 -- ROM D7

CPU D1 -- ROM D1

CPU D2 -- ROM D2

CPU D3 -- ROM D4

CPU D4 -- ROM D3

CPU D5 -- ROM D5

CPU D6 -- ROM D6

CPU D7 -- ROM D0Maybe they did this on purpose to avoid copyright somehow?

In the end the ROMs are almost identical to Apple's.

I dumped the ROMs and was confused - I expected almost identical to Apple II+ ROMs, but they are completely different.

And they don't match what the computer sees in monitor either.

I first assumed I goofed up the wiring on the ROM dumper, but no - dumped some other ROMs and they matched the expected images exactly.

Then assumed it was address lines not as expected, but nope - cheap logic analyzer on the data lines showed the expected ROM did send 1 thing out and the CPU got something different.

Ahah, take another look at comparing the binary of the monitor dump and the ROM dump and figure out the line flipping.

Sheesh