Eudimorphodon

Veteran Member

I apologize for posting such an elementary question but I'm pretty new to designing digital circuitry (I can *kind* of troubleshoot existing stuff, but it's been a while?) and I figure someone here can answer this easily off the top of their heads.

When looking at addresses on the PC bus the logic level is HIGH for a "one" bit and LOW for a "zero", correct? IE, if the computer is operating within the bottom 64K of RAM the state of A19-A16 (highest to the left) will be:

L L L L

while if it's within the page that ends right under the 256k mark they're going to be:

L L H H

And when it rolls over into the 256K block it will be:

L H L L

yes? That's what it seems to say in the hardware manual for my Tandy 1000 EX and I think I've convinced myself that's right based on scratching my head over schematics for existing boards but my rusty brain insists on getting confused by the fact that most chip enables are "LOW", not "HIGH" (IE, the intuitive state of what constitutes a zero or one is sort of flipped?) I've about gotten the point where I want to break in my newly downloaded copy of KiCad and just want to make sure I don't make stupid mistakes in interpreting truth tables.

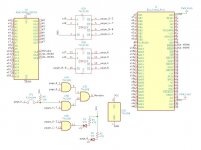

(Disclosure, the project in question is an idea for a 640/704k memory backfill card for Tandy EX/HXes using only three chips. Nothing really new but you have to start somewhere.)

When looking at addresses on the PC bus the logic level is HIGH for a "one" bit and LOW for a "zero", correct? IE, if the computer is operating within the bottom 64K of RAM the state of A19-A16 (highest to the left) will be:

L L L L

while if it's within the page that ends right under the 256k mark they're going to be:

L L H H

And when it rolls over into the 256K block it will be:

L H L L

yes? That's what it seems to say in the hardware manual for my Tandy 1000 EX and I think I've convinced myself that's right based on scratching my head over schematics for existing boards but my rusty brain insists on getting confused by the fact that most chip enables are "LOW", not "HIGH" (IE, the intuitive state of what constitutes a zero or one is sort of flipped?) I've about gotten the point where I want to break in my newly downloaded copy of KiCad and just want to make sure I don't make stupid mistakes in interpreting truth tables.

(Disclosure, the project in question is an idea for a 640/704k memory backfill card for Tandy EX/HXes using only three chips. Nothing really new but you have to start somewhere.)

Last edited: