Dwight Elvey

Veteran Member

Hi

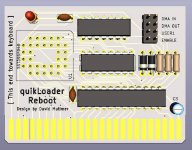

I'm still hoping to find a manual for this board.

It is cool. It allows on to put most anything

that can be loaded from disk onto EPROMs

and then transfered to RAM from the card.

So far, I've been able to use it with what is on

it but I'd like to do some of my own code for

it. With out instructions, it'll be tough.

Cool thing is it has both DOS3.3 and ProDOS

in the EPROMs.

Dwight

I'm still hoping to find a manual for this board.

It is cool. It allows on to put most anything

that can be loaded from disk onto EPROMs

and then transfered to RAM from the card.

So far, I've been able to use it with what is on

it but I'd like to do some of my own code for

it. With out instructions, it'll be tough.

Cool thing is it has both DOS3.3 and ProDOS

in the EPROMs.

Dwight